In What Register Will The Quotient Of The Following Instruction Be Found?

Assembly - Arithmetic Instructions

The INC Didactics

The INC instruction is used for incrementing an operand past i. Information technology works on a single operand that can exist either in a register or in memory.

Syntax

The INC instruction has the following syntax −

INC destination

The operand destination could be an 8-bit, 16-flake or 32-bit operand.

Example

INC EBX ; Increments 32-bit register INC DL ; Increments viii-bit annals INC [count] ; Increments the count variable

The Dec Teaching

The DEC instruction is used for decrementing an operand by one. It works on a single operand that tin can exist either in a register or in memory.

Syntax

The Dec instruction has the following syntax −

DEC destination

The operand destination could be an 8-bit, 16-flake or 32-bit operand.

Example

segment .data count dw 0 value db 15 segment .text inc [count] dec [value] mov ebx, count inc word [ebx] mov esi, value dec byte [esi]

The Add together and SUB Instructions

The ADD and SUB instructions are used for performing elementary addition/subtraction of binary data in byte, word and doubleword size, i.due east., for adding or subtracting eight-bit, 16-bit or 32-bit operands, respectively.

Syntax

The Add and SUB instructions accept the following syntax −

ADD/SUB destination, source

The Add together/SUB pedagogy tin can have place betwixt −

- Annals to annals

- Memory to annals

- Register to memory

- Register to constant information

- Retention to constant data

However, like other instructions, retentiveness-to-memory operations are not possible using ADD/SUB instructions. An ADD or SUB operation sets or clears the overflow and behave flags.

Example

The following example will ask two digits from the user, store the digits in the EAX and EBX register, respectively, add together the values, store the upshot in a memory location 'res' and finally display the result.

SYS_EXIT equ ane SYS_READ equ 3 SYS_WRITE equ 4 STDIN equ 0 STDOUT equ ane segment .data msg1 db "Enter a digit ", 0xA,0xD len1 equ $- msg1 msg2 db "Please enter a 2d digit", 0xA,0xD len2 equ $- msg2 msg3 db "The sum is: " len3 equ $- msg3 segment .bss num1 resb two num2 resb 2 res resb 1 section .text global _start ;must exist declared for using gcc _start: ;tell linker entry point mov eax, SYS_WRITE mov ebx, STDOUT mov ecx, msg1 mov edx, len1 int 0x80 mov eax, SYS_READ mov ebx, STDIN mov ecx, num1 mov edx, ii int 0x80 mov eax, SYS_WRITE mov ebx, STDOUT mov ecx, msg2 mov edx, len2 int 0x80 mov eax, SYS_READ mov ebx, STDIN mov ecx, num2 mov edx, 2 int 0x80 mov eax, SYS_WRITE mov ebx, STDOUT mov ecx, msg3 mov edx, len3 int 0x80 ; moving the starting time number to eax register and second number to ebx ; and subtracting ascii '0' to convert it into a decimal number mov eax, [num1] sub eax, '0' mov ebx, [num2] sub ebx, '0' ; add eax and ebx add eax, ebx ; add '0' to to convert the sum from decimal to ASCII add together eax, '0' ; storing the sum in memory location res mov [res], eax ; impress the sum mov eax, SYS_WRITE mov ebx, STDOUT mov ecx, res mov edx, 1 int 0x80 exit: mov eax, SYS_EXIT xor ebx, ebx int 0x80

When the to a higher place code is compiled and executed, information technology produces the following result −

Enter a digit: three Please enter a second digit: 4 The sum is: seven

The programme with hardcoded variables −

section .text global _start ;must be alleged for using gcc _start: ;tell linker entry point mov eax,'3' sub eax, '0' mov ebx, '4' sub ebx, '0' add eax, ebx add eax, '0' mov [sum], eax mov ecx,msg mov edx, len mov ebx,1 ;file descriptor (stdout) mov eax,four ;arrangement call number (sys_write) int 0x80 ;call kernel mov ecx,sum mov edx, 1 mov ebx,1 ;file descriptor (stdout) mov eax,4 ;arrangement phone call number (sys_write) int 0x80 ;call kernel mov eax,1 ;system call number (sys_exit) int 0x80 ;call kernel section .information msg db "The sum is:", 0xA,0xD len equ $ - msg segment .bss sum resb 1

When the above code is compiled and executed, it produces the following result −

The sum is: vii

The MUL/IMUL Didactics

There are ii instructions for multiplying binary data. The MUL (Multiply) education handles unsigned data and the IMUL (Integer Multiply) handles signed data. Both instructions affect the Carry and Overflow flag.

Syntax

The syntax for the MUL/IMUL instructions is as follows −

MUL/IMUL multiplier

Multiplicand in both cases volition be in an accumulator, depending upon the size of the multiplicand and the multiplier and the generated production is too stored in two registers depending upon the size of the operands. Following section explains MUL instructions with three different cases −

| Sr.No. | Scenarios |

|---|---|

| 1 | When two bytes are multiplied − The multiplicand is in the AL register, and the multiplier is a byte in the retention or in another register. The product is in AX. High-order 8 bits of the production is stored in AH and the depression-lodge eight bits are stored in AL. |

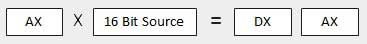

| ii | When ii one-discussion values are multiplied − The multiplicand should be in the AX register, and the multiplier is a word in memory or another register. For case, for an instruction similar MUL DX, y'all must store the multiplier in DX and the multiplicand in AX. The resultant production is a doubleword, which will need ii registers. The loftier-order (leftmost) portion gets stored in DX and the lower-order (rightmost) portion gets stored in AX. |

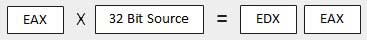

| 3 | When 2 doubleword values are multiplied − When ii doubleword values are multiplied, the multiplicand should be in EAX and the multiplier is a doubleword value stored in memory or in another register. The product generated is stored in the EDX:EAX registers, i.e., the high social club 32 bits gets stored in the EDX register and the depression order 32-bits are stored in the EAX register. |

Example

MOV AL, 10 MOV DL, 25 MUL DL ... MOV DL, 0FFH ; DL= -1 MOV AL, 0BEH ; AL = -66 IMUL DL

Case

The following instance multiplies 3 with 2, and displays the result −

section .text global _start ;must exist declared for using gcc _start: ;tell linker entry signal mov al,'three' sub al, '0' mov bl, '2' sub bl, '0' mul bl add al, '0' mov [res], al mov ecx,msg mov edx, len mov ebx,1 ;file descriptor (stdout) mov eax,4 ;system call number (sys_write) int 0x80 ;call kernel mov ecx,res mov edx, i mov ebx,1 ;file descriptor (stdout) mov eax,4 ;system call number (sys_write) int 0x80 ;call kernel mov eax,one ;system call number (sys_exit) int 0x80 ;call kernel department .data msg db "The event is:", 0xA,0xD len equ $- msg segment .bss res resb 1

When the higher up lawmaking is compiled and executed, it produces the following event −

The effect is: 6

The DIV/IDIV Instructions

The partition functioning generates two elements - a quotient and a residuum. In example of multiplication, overflow does not occur considering double-length registers are used to proceed the product. However, in case of division, overflow may occur. The processor generates an interrupt if overflow occurs.

The DIV (Divide) instruction is used for unsigned information and the IDIV (Integer Split) is used for signed information.

Syntax

The format for the DIV/IDIV educational activity −

DIV/IDIV divisor

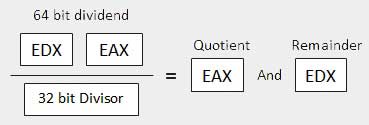

The dividend is in an accumulator. Both the instructions can piece of work with eight-chip, 16-bit or 32-chip operands. The operation affects all half-dozen status flags. Following section explains three cases of division with different operand size −

| Sr.No. | Scenarios |

|---|---|

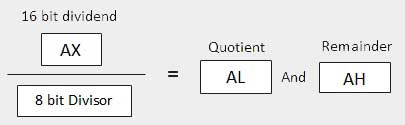

| i | When the divisor is 1 byte − The dividend is assumed to be in the AX register (16 bits). Subsequently division, the quotient goes to the AL annals and the remainder goes to the AH register. |

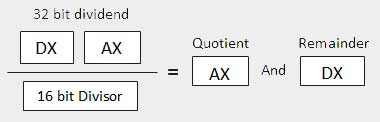

| 2 | When the divisor is 1 word − The dividend is causeless to be 32 bits long and in the DX:AX registers. The high-guild 16 $.25 are in DX and the low-society 16 bits are in AX. After segmentation, the sixteen-bit quotient goes to the AX register and the 16-scrap balance goes to the DX register. |

| three | When the divisor is doubleword − The dividend is assumed to exist 64 bits long and in the EDX:EAX registers. The high-order 32 bits are in EDX and the low-order 32 bits are in EAX. After division, the 32-flake caliber goes to the EAX annals and the 32-fleck balance goes to the EDX register. |

Example

The following example divides 8 with 2. The dividend 8 is stored in the sixteen-fleck AX register and the divisor 2 is stored in the 8-flake BL register.

section .text global _start ;must be declared for using gcc _start: ;tell linker entry point mov ax,'viii' sub ax, '0' mov bl, '2' sub bl, '0' div bl add ax, '0' mov [res], ax mov ecx,msg mov edx, len mov ebx,1 ;file descriptor (stdout) mov eax,4 ;system telephone call number (sys_write) int 0x80 ;call kernel mov ecx,res mov edx, 1 mov ebx,1 ;file descriptor (stdout) mov eax,4 ;arrangement call number (sys_write) int 0x80 ;call kernel mov eax,1 ;arrangement call number (sys_exit) int 0x80 ;call kernel department .information msg db "The result is:", 0xA,0xD len equ $- msg segment .bss res resb i

When the above code is compiled and executed, it produces the following result −

The upshot is: 4

Useful Video Courses

Video

Video

In What Register Will The Quotient Of The Following Instruction Be Found?,

Source: https://www.tutorialspoint.com/assembly_programming/assembly_arithmetic_instructions.htm

Posted by: murphyature1962.blogspot.com

0 Response to "In What Register Will The Quotient Of The Following Instruction Be Found?"

Post a Comment